Interface de communication I2C

20 octobre 2023

Dans le domaine des systèmes embarqués et de l'électronique, une communication efficace entre les composants est essentielle. Parmi les nombreux protocoles de communication disponibles aujourd'hui, le protocole I2C (Inter-Integrated Circuit) se distingue comme un choix populaire auprès de nombreux ingénieurs et développeurs en raison de sa simplicité, de sa flexibilité et de sa faible consommation d'énergie.

Dans cet article :

Qu'est-ce que l'I2C ?

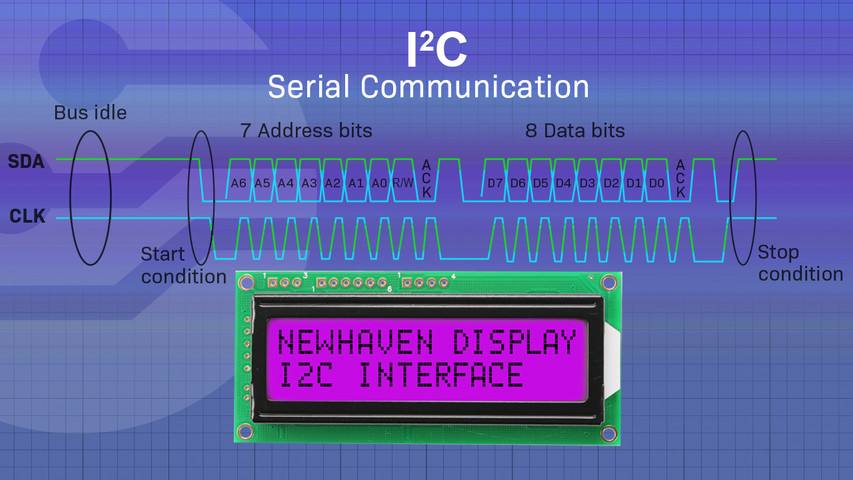

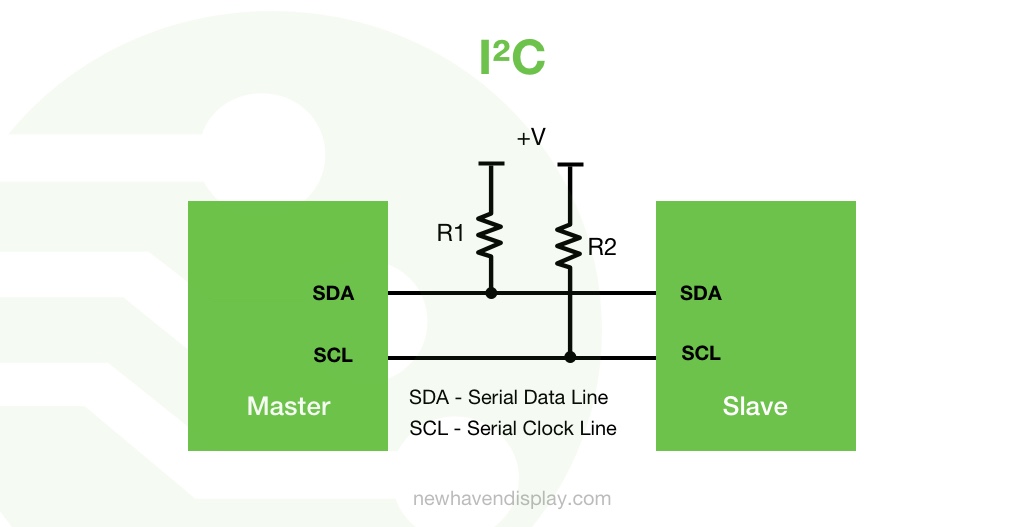

Inter-Integrated Circuit, abrégé I²C (prononcé « I-squared-C » ou « I-two-C »), est un protocole de communication série largement adopté, caractérisé par sa conception de bus série asymétrique multi-maîtres, multi-esclaves, adapté à la communication sur de courtes distances. La particularité de l'I2C est qu'il n'utilise que deux fils pour la communication, SDA (Serial Data) et SCL (Serial Clock), ce qui simplifie les connexions et permet de gagner de la place.

Bien que la notation officielle soit « I²C », prononcée « eye-squared-see », nous l'appellerons « I2C » pour plus de simplicité. Le symbole ² est un exposant 2, ce qui signifie que le I est multiplié par lui-même deux fois. Il s'agit d'une référence aux deux fils utilisés pour la communication.

Caractéristiques I2C :

- I2C est un protocole de communication de données série synchrone.

- Utilise seulement deux fils pour la communication : données série et horloge série.

- Prend en charge plusieurs maîtres et plusieurs esclaves sur le même bus.

- Transmission semi-duplex - La communication entre le dispositif maître et le dispositif esclave peut s'effectuer dans les deux sens, mais pas simultanément.

- Allongement de l'horloge - Un périphérique esclave peut maintenir la ligne d'horloge afin de disposer de plus de temps pour traiter les données.

- Arbitrage - Si deux maîtres commencent la transmission en même temps, I2C dispose d'une méthode intégrée pour décider lequel des deux maîtres continue et lequel attend, garantissant ainsi l'intégrité des données.

- Système d'adressage 7 bits, mais pouvant également prendre en charge les adresses 10 bits.

- Prend en charge différentes vitesses - La spécification I2C standard définit quatre niveaux de vitesse : mode standard (100 kbps), mode rapide (400 kbps), mode rapide Plus (1 Mbps) et mode haute vitesse (3,4 Mbps).

En savoir plus:Communication série ou parallèle

Comment fonctionne I2C ?

I2C est un bus série à deux fils qui utilise deux lignes bidirectionnelles à drain ouvert, SDA et SCL, toutes deux tirées vers le haut.

- SDA (ligne de données série): cette ligne transporte les données.

- SCL (Serial Clock Line): cette ligne assure la synchronisation.

Les périphériques sur le bus I2C peuvent être soit maîtres, soit esclaves :

- Maître (contrôleur) : lance et contrôle le transfert de données sur le bus.

- Esclave (périphérique) : répond au maître.

Les termes « maître » et « esclave » ont été utilisés historiquement pour décrire les rôles des périphériques sur le bus I2C, mais ils ont été remplacés principalement par « contrôleur » et « périphérique » dans de nombreux contextes.

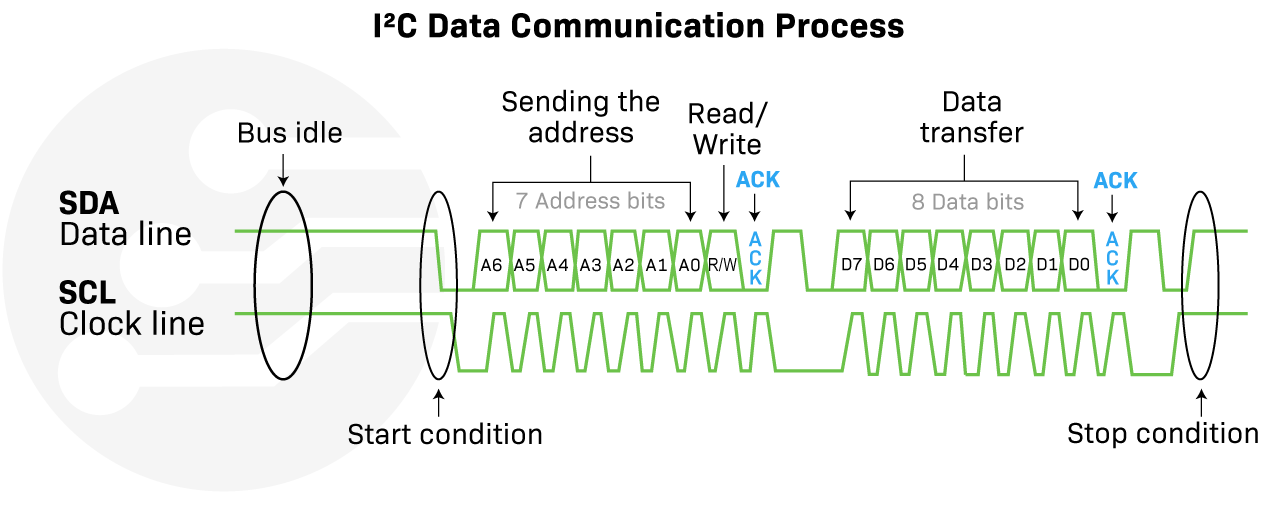

Processus de communication de données I2C

- État de ralenti du bus (bus libre):

- Avant le début de toute communication, les lignes SDA (ligne de données série) et SCL (ligne d'horloge série) restent toutes deux à un niveau haut, indiquant que le bus est inactif.

- Condition de démarrage:

- Initiée par le maître, une condition de démarrage se produit lorsque la ligne SDA passe de haut à bas alors que la ligne SCL est haute. Cela signale à tous les appareils esclaves que la communication est sur le point de commencer.

- Envoi de l'adresse:

- Le dispositif maître envoie une adresse à 7 bits au dispositif esclave avec lequel il souhaite communiquer. Celle-ci est suivie d'un 8e bit, le bit lecture/écriture (R/W), qui indique le sens de l'opération :

0pour écrire et1à lire. - Cette séquence combinée de 8 bits est appelée trame d'adresse.

- Dans le cas particulier des adresses 10 bits, le maître envoie 2 octets. Le premier octet commence par 11110, suivi des bits 9 et 8 de l'adresse 10 bits, puis du bit R/W. Le deuxième octet contient les bits 7 à 0 de l'adresse 10 bits.

- Le dispositif maître envoie une adresse à 7 bits au dispositif esclave avec lequel il souhaite communiquer. Celle-ci est suivie d'un 8e bit, le bit lecture/écriture (R/W), qui indique le sens de l'opération :

- Bit d'accusé de réception (ACK):

- Une fois l'adresse et les bits R/W envoyés, le maître libère la ligne SDA. Le dispositif esclave adressé tire la ligne SDA vers le bas (bit d'accusé de réception) pour confirmer qu'il a bien reçu son adresse et qu'il est prêt à communiquer.

- Transfert de données:

- Pour une opération d'écriture, le maître envoie un octet de données à l'esclave. L'esclave accuse réception en mettant la ligne SDA à l'état bas pendant une impulsion d'horloge.

- Pour une opération de lecture, l'esclave envoie un octet de données au maître. Le maître accuse réception, mais libère la ligne SDA (un NACK ou aucune confirmation) après le dernier octet pendant une opération de lecture, signalant à l'esclave d'arrêter d'envoyer des données.

- Condition d'arrêt:

- Pour mettre fin à une session de communication, le maître génère une condition d'arrêt en faisant passer la ligne SDA de l'état bas à l'état haut tandis que la ligne SCL est à l'état haut. Après la condition d'arrêt, le bus revient à l'état inactif.

- Le maître peut également générer une condition de démarrage répétée afin de conserver le contrôle du bus pour une autre opération de lecture ou d'écriture. Cette fonction est souvent utilisée dans des opérations plus complexes, telles que la modification du sens des données sans libérer le bus.

En savoir plus:Qu'est-ce que le débit en bauds?

Adressage de plusieurs esclaves

S'il y a plusieurs périphériques esclaves, le maître communique avec chacun d'eux en utilisant leur adresse unique. Seul l'esclave dont l'adresse correspond répond et communique, tandis que les autres ignorent les messages.

Allongement de l'horloge

Un esclave peut maintenir la ligne SCL enfoncée (un processus appelé « clock stretching ») s'il a besoin de plus de temps pour traiter une instruction ou récupérer des données. Le maître doit attendre que la ligne SCL soit relâchée avant de pouvoir continuer.

Arbitrage de bus (pour multi-maîtres)

L'arbitrage est le processus qui consiste à déterminer quel dispositif maître prend le contrôle du bus lorsque plusieurs maîtres tentent d'établir une communication simultanément ou dans un laps de temps très court. I2C prend en charge plusieurs maîtres, ce qui signifie que plusieurs maîtres peuvent tenter de contrôler le bus à un moment donné sans corrompre le message.

Procédure d'arbitrage I2C :

- Lorsqu'un maître commence une transmission, il suppose qu'il a le contrôle du bus.

- Lorsqu'il envoie les bits d'adresse et de données, il vérifie la ligne SDA après avoir écrit chaque bit. S'il écrit un

0et relit un1, il sait qu'un autre maître a pris le contrôle et se retire, perdant ainsi l'arbitrage. - Le maître qui a perdu l'arbitrage cesse immédiatement de transmettre et attend que la ligne SCL (Serial Clock) passe à l'état HAUT, indiquant la fin du transfert en cours, avant de réessayer.

Grâce à un transfert de données efficace utilisant seulement deux fils, I2C est devenu une interface de communication série très prisée pour les systèmes recherchant une communication fiable et économique.

En savoir plus:Exemple de code pour implémenter I2C sur un écran LCD COG 16x2

Avantages de l'I2C :

- Simplicité: ne nécessite que deux fils, quel que soit le nombre d'appareils connectés.

- Flexibilité: prend en charge plusieurs maîtres et esclaves.

- Efficacité énergétique: les périphériques I2C peuvent être mis hors tension lorsqu'ils ne sont pas utilisés sans affecter le bus.

- Adressage intégré: chaque périphérique sur le bus possède une adresse unique.

- Largement pris en charge: de nombreux microcontrôleurs et périphériques sont équipés d'interfaces matérielles I2C intégrées, ce qui facilite l'intégration.

- Modes de vitesse flexibles: I2C prend en charge plusieurs modes de vitesse.

Inconvénients de l'I2C :

- Limitations de vitesse: généralement plus lent que d'autres protocoles tels que SPI.

- Limites de distance: le protocole I2C est conçu pour les courtes distances. Pour les distances plus longues, l'intégrité du signal et le bruit peuvent poser problème.

- Complexité des grands réseaux: à mesure que de nouveaux appareils sont ajoutés, l'adressage peut devenir compliqué.

- Pas de vérification des erreurs: ne dispose pas d'un mécanisme intégré de vérification des erreurs.

- Asymétrique: pas de signalisation différentielle, ce qui pourrait améliorer l'immunité au bruit.

I2C par rapport aux autres protocoles de communication série

Lorsque vous choisissez un protocole de communication série pour votre projet, il est important de tenir compte des besoins spécifiques de votre application. Bien que le protocole I2C soit très répandu, il existe d'autres protocoles disponibles, tels que SPI, RS-232, CAN et UART. Chaque protocole présente ses propres avantages et inconvénients. Il est donc important de peser le pour et le contre avant de prendre une décision.

I2C vs SPI (interface périphérique série) :

- Câbles : SPI nécessite davantage de câbles : SCLK (horloge série), MOSI (sortie maître/entrée esclave), MISO (entrée maître/sortie esclave) et un SS (sélection esclave) unique pour chaque appareil. En revanche, I2C ne nécessite que SDA et SCL.

- Vitesse : SPI peut être plus rapide que I2C car il n'y a pas de phase d'adresse dans la transmission des données.

- Flexibilité : alors que le protocole I2C prend en charge nativement la configuration multi-maître, ce n'est pas le cas du protocole SPI.

I2C vs UART (récepteur-émetteur asynchrone universel) :

- Complexité du protocole : l'UART est plus simple, car il ne concerne que deux appareils qui communiquent entre eux à l'aide de deux lignes (TX et RX). L'I2C peut connecter plusieurs appareils à l'aide de seulement deux lignes.

- Synchronisation : UART est asynchrone (pas de ligne d'horloge), tandis que I2C est synchrone (nécessite une ligne d'horloge).

I2C vs CAN (réseau local de contrôleurs) :

- Cas d'utilisation : CAN est conçu pour les véhicules et les systèmes industriels où la fiabilité dans des conditions bruyantes est cruciale. I2C est davantage destiné à la communication embarquée à courte distance entre les circuits intégrés.

- Fiabilité : CAN dispose de mécanismes intégrés de vérification et de correction des erreurs, contrairement à I2C.

I2C vs RS232 :

- RS232 utilise 3 fils et ne prend en charge que deux appareils (un émetteur et un récepteur), tandis que I2C prend en charge plusieurs appareils avec seulement 2 fils.

- Le RS-232 est adapté aux communications longue distance.

| Protocole | Nombre de fils | Vitesse | Complexité | Consommation électrique | Applications courantes |

|---|---|---|---|---|---|

| I2C | 2 | Lent | Moyen | Faible | Systèmes embarqués, capteurs, écrans, actionneurs, périphériques. |

| SPI | 4 | Rapidement | Moyen | Moyen | Communication à haut débit, puces mémoire. |

| UART | 2 | Lent | Faible | Faible | Communication asynchrone, communication série sur de longues distances. |

| CAN | 2 | Rapidement | Moyen | Moyen | Applications automobiles et industrielles. |

| RS-232 | 3 | Lent | Moyen | Moyen | Ordinateurs, imprimantes, modems. |

Conclusion

I2C est un protocole de communication indispensable qui a fait ses preuves depuis des décennies dans le monde de l'électronique. Sa simplicité, combinée à sa capacité à connecter plusieurs appareils à l'aide de seulement deux lignes, en fait un choix populaire pour de nombreuses applications. Cependant, comme tout protocole, il a ses limites et n'est pas idéal dans tous les cas de figure. Lors de la conception d'un système, il convient d'évaluer les besoins spécifiques de l'application et de choisir le protocole de communication qui correspond le mieux à ces besoins.